焊珠探针技术(bead probe)是由Agilent(安捷伦,现已改为是德科技(Keysight Technologies))独家申请专利所提出,在不需要额外增加电路板空间的情况下,使用现有佈线来增加ICT(In-Circuit-Test)的测试点涵盖率(coverage),也就是增加印刷电路板上的测试点(Test Point),以达到组装电路板可以使用ICT测试的目的。

相关阅读: PCB电路板为何要有测试点?

因为现在电路板上面的零件密度越来越密,但是空间却越来越小,尤其是做手机的板子,所以最先被牺牲的就是不具任何功能作用的测试点,因为很多老闆都认为:「品质是制造出来的,所以只要把电路板组装的品质做好,就不需要有后续的电气测试了。」。这句话我完全同意(站在老闆的立场XD),只是以目前电子业快速前进的步调,九个月甚至六个月就要完成一个案子,真不知道有那个工程师可以打包票,说他设计出来的产品没有Bug,组装厂也不敢说他们组装零的板子可以零缺点?到现在BGA封装都已经够让SMT与制程工程师头大了,现在又出现了一堆新的IC封装(如QFN),还有把整个通讯模组作在一块小电路板上面,成品厂需要把这整块模组电路板当成SMT零件,焊接在其电路板上的情况。

种种设计与组装上的挑战,都在在现显示很难捨弃传统的ICT,而纯粹只使其他的方法(如AOI, AXI)来确保组装电路板(PCB Assembly)的品质,于是有越来越多的公司又开始回来使用ICT,只是电路板上的空间只会越来越小,哪还有空间可以摆放测试点,所以聪明的安捷伦就想出了这种在既有佈线(trace)上面印刷锡膏的方式来取代测试点的「焊珠探针技术(bead probe)」方法,安捷伦的目的当然是希望整个电子业可以继续保有ICT作业,然后购买更多它的3070系列ICT测试机台。

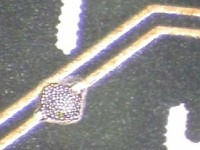

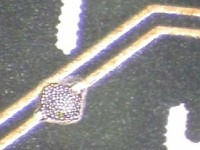

传统的ICT测试方式,使用尖头的探针接触在圆形的测试点上面以形成迴路,这种方式需要的是一个大面积的测试点,然后探针就像是射箭一样的必须射到标靶范围内,所以需要使用较多的电路板空间;而焊珠探针技术(bead probe)则刚好颠倒,它希望测试点尽量不要佔用电路板的空间,但为了可以与探针接触形成迴路,于是印刷了锡膏,让测试点变高,然后使用直径较大的平头探针(50, 75,100 mils)来增加与测试点接触的机会,就像拿着榔头敲铁钉一般。

理论上这真的是测试点重生的一大突破,但在现实环境上还有很多的技术需要克服:

-

佈线上面印刷锡膏容易因为助焊剂的残留而影响到探针与测试点接触不良的问题产生。针对这个问题,目前已有多家的探针制造商设计出设合焊珠探针技术(bead probe)使用的探针。

(下面探针的图片取自 ingun 公司)

-

锡膏的印刷要非常精准。尤其是无铅的锡膏内聚力比锡铅的锡膏来得差,需要更精准的锡膏印刷,因为锡高的印刷量会决定焊锡的高度,测试点上的焊锡高如果不够,ICT的误判率就会增加。这点牵涉到锡膏的印刷工艺、钢板的精度,还有电路板拼板时的公差。

-

佈线的宽度如果太小,容易因为附着力不足而被探针或是其他的外力不小心推断掉。一般建议最小佈线宽度要有5mils以上。据说目前有业者成功的测试过4mils,但随着佈线的宽度越小,其ICT的误判率就越高。建议可以把佈线的宽度加大,然后周围用绿漆(mask)盖起来,这样会比较强壮。

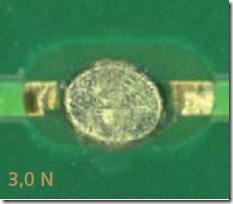

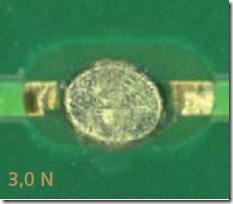

(下面焊珠的图片也是取自 ingun 公司,这些焊珠已经过探针接触挤压,左边为施加2.0N右边为施加3.0N以后的焊珠形状)

-

使用焊珠探针技术(bead probe)是否会影响到高频的品质。根据安捷伦的测试报告是不会影响到高频的performance。

-

使用焊珠探针技术(bead probe)是否会有电容效应或是天线效应。根据安捷伦的回覆,目前的测试与客户的反应皆没有听说有这方面的问题。

-

焊珠探针技术(bead probe)的可靠度为何?根据安捷伦的回覆,测试过200个cycles没有问题。

另外,安捷伦强烈建议工厂导入这种焊珠探针技术(bead probe)技术,最好要有六个月以上的实验期,因为需要选择锡膏、微调钢板开孔、锡膏量,与还要调整ICT测试探针种类与精度。所以在初期实验的时候,最好可以在电路板上同时存在传统的圆形测试点与新的焊珠测试点。

延伸阅读:

电路板组装后测试方法探讨

简介电路板组装后的功能测试(FVT/FCT)

产品烧机的优缺点探讨 (B/I, Burn In),Run/In又是什么?

贊助商广告

PayPal

欧付宝

此技术很好,但是弊端如何规避?

1、测试接触焊珠后,因焊珠上有助焊剂会粘到测试针上,时间长了会影响测试接触效果,也有测试针被堵死的风险。

2、怎么保证测试针和bead点的位置精度。

Reply

日月,

你的问题其实不难,这些

1. 早期一面SMT一面波焊的时候就有这个问题,解决方法就是选用尖探针、找锡膏厂商降低助焊剂残留、清洗。

2. 这个与探针及测试点的对位道理是一样的。

Reply

上述 图面中ingun 设计的探针,实际体验如何,我们工厂没用过这种设计?大家有使用的经验吗

//m.letratesoro.com/wp-content/uploads/images/bead-probe_104A9/bead_probe_tip01.jpg

//m.letratesoro.com/wp-content/uploads/images/bead-probe_104A9/bead_probe_tip02.jpg

Reply

Lenovo,

Sorry! 还没有实际使用过。

Reply

一直很感谢楼主分享自己的经验,就这次的标题,个人也有些观点。

1。此方法相比传统ICT要好的多,而且并不影响高速信号的完整性,反而比传统信号眼图要好看的多

2。现在BGA零件越来越多,尤其是像DDR这些高速trace传统一般不加测点,这个方法在不影响信号的情况下,反而会增加Boundary Scan Testing等等测试项目,以确保产品尤其是BGA那种IC的焊接or可靠性质量

3。针对误测或复测率问题,建议是同一个trace放>=2的测点,而ICT也同时要有2个同路径的顶针,就我司改善的效果复测率明显降低(总有一个会被顶到)

4。此方法也是爲了避免传统圆盘式(一般比trace宽的多)测点容易产生寄生电容or电感,影响高速信号的品质,而现行方法只是在trace上打开mask层,锡珠的测点和trace等宽

5。这个设备投资真的是很巨大的,尤其是使用安捷伦的设备,如果一个公司用这些设备得话,说明其(or客户)对产品质量真的非常看重,相应其出货的产品可靠度非常高

Reply

戈兰德;

使用两个以上的 bead probe 在同一线路的确是个不错的建议,也应该可以大大降低误判率。谢谢你提供的经验。

Reply

这个方式的确是增加ICT测试涵盖率的一个好方法

我在某公司服务的时候,该公司就有导入此方式增加ICT的涵盖率

测点上锡是可以保护测点不被测针扎穿或保护测点不会氧化的一个方法

但是也会造成以下问题的产生

1.因上锡后的测点因flux残留过多或是flux过硬导致测针无法扎穿flux所造成的误测

2.锡点是圆弧面,因PCB or 测具测针位置的公差问题导致测针顺着圆弧面滑脱造成误测

这两个问题点是ICT工程师要克服的问题

Reply

Flux及探针的准确度的确是ICT的问题,所以有公司专门设计多爪的大头探针。如 ingun 就有特别出给 bread probe 的探针。

Reply